# **Embedded electronics**

Rémi Parrot remi.parrot@ec-nantes.fr

## Overview

References

Content

Boolean Algebra

VHDL

Introduction

Code structure

Data types

Operators

Concurrent code

Sequential code

Composition

Mealy and Moore Machines

Conclusion

# References

\_\_\_\_

- Previous teacher: Joumana Lagha

- Circuit Design with VHDL, by Volnei A. Pedroni

# Content

\_

- Lecture + tutorials : 12h

- Lab : 20h

- Exam : 2h

# Content

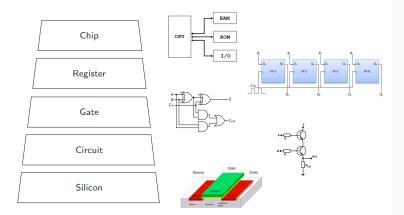

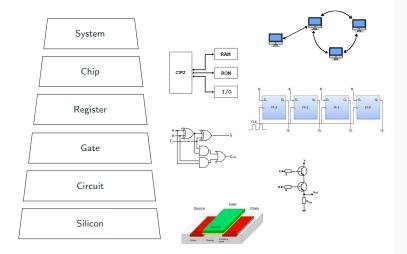

• Designing Circuit

- Designing Circuit

- Analog circuit Logic circuit

- Designing Circuit

- Analog circuit Logic circuit

- Boolean Algebra

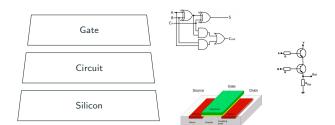

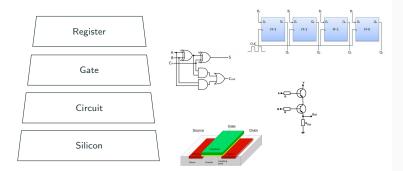

- Designing Circuit

- Analog circuit Logic circuit

- Boolean Algebra

- Description Language : VHDL

Silicon

# **Boolean Algebra**

$\begin{array}{l} \mbox{Logic Variable} \\ \mbox{Variable that can take 2 values ("true" or "false")} \end{array}$

- "false" is noted 0

- "true" is noted 1

### Logic Variable

Variable that can take 2 values ("true" or "false")

- "false" is noted 0

- "true" is noted 1

### Logic Function

Function on logic variables

- input: some logic variables;

- *output*: one logic value.

### Logic Variable

Variable that can take 2 values ("true" or "false")

- "false" is noted 0

- "true" is noted 1

### Logic Function

Function on logic variables

- input: some logic variables;

- *output*: one logic value.

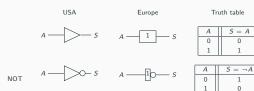

#### Example

With only 1 input:

|   | constant | constant | identity | negation        |

|---|----------|----------|----------|-----------------|

| A | f(A)=0   | f(A) = 1 | f(A) = A | $f(A) = \neg A$ |

| 0 | 0        | 1        | 0        | 1               |

| 1 | 0        | 1        | 1        | 0               |

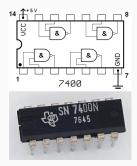

Logic Gates

|      |                         | A&                              | A<br>0 | <i>B</i> | S = A.B                     |

|------|-------------------------|---------------------------------|--------|----------|-----------------------------|

| AND  | A = -s                  | $\hat{B}$ $ S$                  | 0      | 1        | 0                           |

| AND  |                         |                                 | 1      | 0        | 0                           |

|      |                         |                                 | 1      | 1        | 1                           |

|      |                         |                                 | L      | -        |                             |

|      |                         |                                 | A      | В        | $S = \overline{A.B}$        |

|      | A = 0 - s               | $B = {}^{A} - {}^{\&} - {}^{S}$ | 0      | 0        | 1                           |

| NAND |                         | В                               | 0      | 1        | 1                           |

|      |                         |                                 | 1      | 0        | 1                           |

|      |                         |                                 | 1      | 1        | 0                           |

|      |                         |                                 | A      | В        | S = A + B                   |

|      | A = -s                  | $A = \frac{1}{B} \ge 1$ s       | 0      | 0        | 0                           |

| OR   | в                       | B — J                           | 0      | 1        | 1                           |

|      |                         |                                 | 1      | 0        | 1                           |

|      |                         |                                 | 1      | 1        | 1                           |

|      |                         |                                 | A      | В        | $S = \overline{A + B}$      |

|      | A                       | A > 1 .                         |        | в<br>0   | S = A + B<br>1              |

| NOR  | $B \xrightarrow{A} > s$ | B = -s                          | 0      | 1        | 0                           |

| NOR  |                         |                                 | 1      | 0        | 0                           |

|      |                         |                                 | 1      | 1        | 0                           |

|      |                         |                                 |        | 1        | 0                           |

|      |                         |                                 | A      | В        | $S = A \oplus B$            |

|      | A =                     | $A = 1 \qquad S$                | 0      | 0        | 0                           |

| XOR  | ° ¬L                    | В                               | 0      | 1        | 1                           |

|      |                         |                                 | 1      | 0        | 1                           |

|      |                         |                                 | 1      | 1        | 0                           |

|      |                         |                                 |        | В        | $S = \overline{A \oplus B}$ |

|      | A                       | A = 1                           | A<br>0 | 0        | $S = A \oplus B$            |

| XNOR | A = B                   | $\tilde{B} \rightarrow 0 - s$   | 0      | 1        | 0                           |

| ANOR | , <u> </u>              |                                 | 1      | 0        | 0                           |

|      |                         |                                 | 1      | 1        | 1                           |

|      |                         |                                 |        | 1        | 1                           |

8/69

### Some properties

#### Involution

### Commutativity

- A.B = B.A

- A + B = B + A

### Associativity

- A.(B.C) = (A.B).C

- A + (B + C) = (A + B) + C

#### Neutral element

- *A*.1 = *A*

- A + 0 = A

#### Absorbing element

- A.0 = 0

- A + 1 = 1

# • $\overline{\overline{A}} = A$

#### Inverse element

- $A.\overline{A} = 0$

- $A + \overline{A} = 1$

### Idempotence

- A.A = A

- A + A = A

#### Distributivity

• A.(B+C) = A.B + A.C

### Some properties

#### Involution

### Commutativity

- A.B = B.A

- A + B = B + A

### Associativity

- A.(B.C) = (A.B).C

- A + (B + C) = (A + B) + C

#### Neutral element

- *A*.1 = *A*

- A + 0 = A

#### Absorbing element

- A.0 = 0

- A + 1 = 1

# • $\overline{\overline{A}} = A$

#### Inverse element

- $A.\overline{A} = 0$

- $A + \overline{A} = 1$

### Idempotence

- A.A = A

- A + A = A

### Distributivity

• A.(B+C) = A.B + A.C

#### **Morgan Laws**

•  $\overline{A.B} = \overline{A} + \overline{B}$ •  $\overline{A+B} = \overline{A}.\overline{B}$  **Consequence** All logical functions can be built with *NAND gate* (or *NOR gate*).

#### Exercise

Simplify the following expressions:

- 1. A + A.B

- 2. A.(A + B)

- 3.  $(A+B).(A+\overline{B})$

#### Exercise

Simplify the following expressions:

- 1. A + A.B = A.1 + A.B = A.(1 + B) = A.1 = A

- 2. A.(A + B)

- 3.  $(A+B).(A+\overline{B})$

#### Exercise

Simplify the following expressions:

- 1. A + A.B = A.1 + A.B = A.(1 + B) = A.1 = A

- 2. A.(A+B) = A.A + A.B = A + A.B = A

- 3.  $(A+B).(A+\overline{B})$ =  $A.A + A.\overline{B} + B.A + B.\overline{B} = A + A.\overline{B} + A.B + 0 = A.(1+\overline{B}+B) = A.1 = A$

1. Write the truth table of the adder

|    | A | B | R | С |

|----|---|---|---|---|

|    | 0 | 0 | 0 | 0 |

| 1. | 0 | 1 | 1 | 0 |

|    | 1 | 0 | 1 | 0 |

|    | 1 | 1 | 0 | 1 |

1 - 1

1. Write the truth table of the adder

|    | Α | В | R | С |

|----|---|---|---|---|

|    | 0 | 0 | 0 | 0 |

| 1. | 0 | 1 | 1 | 0 |

|    | 1 | 0 | 1 | 0 |

|    | 1 | 1 | 0 | 1 |

- 1. Write the truth table of the adder

- 2. Deduce the logical function R = f(A, B)

|    | A | В | R | С |

|----|---|---|---|---|

|    | 0 | 0 | 0 | 0 |

| 1. | 0 | 1 | 1 | 0 |

|    | 1 | 0 | 1 | 0 |

|    | 1 | 1 | 0 | 1 |

| -  | - |   | _ |   |

2.

$$R = A \oplus B$$

- 1. Write the truth table of the adder

- 2. Deduce the logical function R = f(A, B)

|    | A   | В            | R | С |

|----|-----|--------------|---|---|

|    | 0   | 0            | 0 | 0 |

| 1. | 0   | 1            | 1 | 0 |

|    | 1   | 0            | 1 | 0 |

|    | 1   | 1            | 0 | 1 |

| 2. | R = | $A \oplus E$ | 3 |   |

- 1. Write the truth table of the adder

- 2. Deduce the logical function R = f(A, B)

- 3. Deduce the logical function C = g(A, B)

#### **Exercise** Let's build a *one bit adder* with a carry.

- 1. Write the truth table of the adder

- 2. Deduce the logical function R = f(A, B)

- 3. Deduce the logical function C = g(A, B)

|                     | A | В | R | С |

|---------------------|---|---|---|---|

|                     | 0 | 0 | 0 | 0 |

| 1.                  | 0 | 1 | 1 | 0 |

|                     | 1 | 0 | 1 | 0 |

|                     | 1 | 1 | 0 | 1 |

| 2. $R = A \oplus B$ |   |   |   |   |

3. C = A.B

#### **Exercise** Let's build a *one bit adder* with a carry.

- 1. Write the truth table of the adder

- 2. Deduce the logical function R = f(A, B)

- 3. Deduce the logical function C = g(A, B)

- 4. Draw the full circuit

|    | A   | В            | R | С |

|----|-----|--------------|---|---|

|    | 0   | 0            | 0 | 0 |

| 1. | 0   | 1            | 1 | 0 |

|    | 1   | 0            | 1 | 0 |

|    | 1   | 1            | 0 | 1 |

| 2. | R = | $A \oplus E$ | 3 |   |

3.

$$C = A.B$$

#### **Exercise** Let's build a *one bit adder* with a carry.

- 1. Write the truth table of the adder

- 2. Deduce the logical function R = f(A, B)

- 3. Deduce the logical function C = g(A, B)

- 4. Draw the full circuit

|                     | Α | В | R | С |  |  |

|---------------------|---|---|---|---|--|--|

|                     | 0 | 0 | 0 | 0 |  |  |

| 1.                  | 0 | 1 | 1 | 0 |  |  |

|                     | 1 | 0 | 1 | 0 |  |  |

|                     | 1 | 1 | 0 | 1 |  |  |

| 2. $R = A \oplus B$ |   |   |   |   |  |  |

| 3. $C = A.B$        |   |   |   |   |  |  |

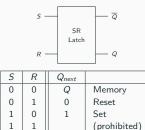

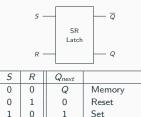

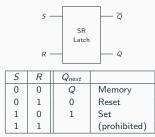

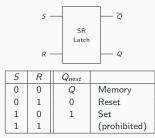

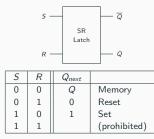

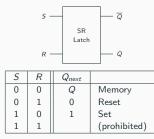

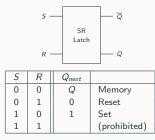

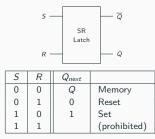

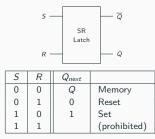

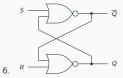

Flip-flop (or latch) A flip-flop is a circuit that has two stables states. It can be used to store information.

#### Exercise

Let's build a simple SR latch.

1. Write the truth table  $Q_{next} = f(S, Q)$

Flip-flop (or latch) A flip-flop is a circuit that has two stables states. It can be used to store information.

#### Exercise

Let's build a simple SR latch.

1. Write the truth table  $Q_{next} = f(S, Q)$

|    | S | Q | Q <sub>next</sub> |

|----|---|---|-------------------|

|    | 0 | 0 | 0                 |

| 1. | 0 | 1 | 1                 |

|    | 1 | 0 | 1                 |

|    | 1 | 1 | 1                 |

Flip-flop (or latch) A flip-flop is a circuit that has two stables states. It can be used to store information.

#### Exercise

- 1. Write the truth table  $Q_{next} = f(S, Q)$

- 2. Deduce the logical function  $Q_{next} = f(S, Q)$

|    | S | Q | Qnext |

|----|---|---|-------|

|    | 0 | 0 | 0     |

| 1. | 0 | 1 | 1     |

|    | 1 | 0 | 1     |

|    | 1 | 1 | 1     |

Flip-flop (or latch) A flip-flop is a circuit that has two stables states. It can be used to store information.

#### Exercise

Let's build a simple SR latch.

1 1

|    | S | Q | Q <sub>next</sub> |

|----|---|---|-------------------|

|    | 0 | 0 | 0                 |

| 1. | 0 | 1 | 1                 |

|    | 1 | 0 | 1                 |

|    | 1 | 1 | 1                 |

2.

$$Q_{next} = S + Q$$

- 1. Write the truth table  $Q_{next} = f(S, Q)$

- Deduce the logical function  $Q_{next} = f(S, Q)$ 2.

#### Flip-flop (or latch)

A flip-flop is a circuit that has two stables states. It can be used to store information.

#### Exercise

Let's build a simple SR latch.

1 1

(prohibited)

|    | S | Q | Q <sub>next</sub> |

|----|---|---|-------------------|

|    | 0 | 0 | 0                 |

| 1. | 0 | 1 | 1                 |

|    | 1 | 0 | 1                 |

|    | 1 | 1 | 1                 |

2.

$$Q_{next} = S + Q$$

- 1. Write the truth table  $Q_{next} = f(S, Q)$

- 2. Deduce the logical function  $Q_{next} = f(S, Q)$

- 3. Write the logical function  $\overline{Q_{next}} = g(S, Q)$

#### Flip-flop (or latch)

A flip-flop is a circuit that has two stables states. It can be used to store information.

#### Exercise

- 1. Write the truth table  $Q_{next} = f(S, Q)$

- 2. Deduce the logical function  $Q_{next} = f(S, Q)$

- 3. Write the logical function  $\overline{Q_{next}} = g(S, Q)$

|    | S | Q | Q <sub>next</sub> |

|----|---|---|-------------------|

|    | 0 | 0 | 0                 |

| 1. | 0 | 1 | 1                 |

|    | 1 | 0 | 1                 |

|    | 1 | 1 | 1                 |

$$2. \quad Q_{next} = S + Q$$

3.

$$\overline{Q_{next}} = \overline{S+Q}$$

#### Flip-flop (or latch)

A flip-flop is a circuit that has two stables states. It can be used to store information.

#### Exercise

- 1. Write the truth table  $Q_{next} = f(S, Q)$

- 2. Deduce the logical function  $Q_{next} = f(S, Q)$

- 3. Write the logical function  $\overline{Q_{next}} = g(S, Q)$

- 4. Write the truth table  $Q_{next} = h(R, \overline{Q})$

|    | S | Q | Q <sub>next</sub> |

|----|---|---|-------------------|

|    | 0 | 0 | 0                 |

| 1. | 0 | 1 | 1                 |

|    | 1 | 0 | 1                 |

|    | 1 | 1 | 1                 |

$$2. \quad Q_{next} = S + Q$$

3.

$$\overline{Q_{next}} = \overline{S+Q}$$

#### Flip-flop (or latch)

A flip-flop is a circuit that has two stables states. It can be used to store information.

#### Exercise

- 1. Write the truth table  $Q_{next} = f(S, Q)$

- 2. Deduce the logical function  $Q_{next} = f(S, Q)$

- 3. Write the logical function  $\overline{Q_{next}} = g(S, Q)$

- 4. Write the truth table  $Q_{next} = h(R, \overline{Q})$

|    | S | Q | Q <sub>next</sub> |

|----|---|---|-------------------|

|    | 0 | 0 | 0                 |

| 1. | 0 | 1 | 1                 |

|    | 1 | 0 | 1                 |

|    | 1 | 1 | 1                 |

$$2. \quad Q_{next} = S + Q$$

3.

$$\overline{Q_{next}} = \overline{S+Q}$$

|    | R | $\overline{Q}$ | Q <sub>next</sub> |

|----|---|----------------|-------------------|

|    | 0 | 0              | 1                 |

| 4. | 0 | 1              | 0                 |

|    | 1 | 0              | 0                 |

|    | 1 | 1              | 0                 |

#### Flip-flop (or latch)

A flip-flop is a circuit that has two stables states. It can be used to store information.

#### Exercise

- 1. Write the truth table  $Q_{next} = f(S, Q)$

- 2. Deduce the logical function  $Q_{next} = f(S, Q)$

- 3. Write the logical function  $\overline{Q_{next}} = g(S, Q)$

- 4. Write the truth table  $Q_{next} = h(R, \overline{Q})$

- 5. Deduce the logical function  $Q_{next} = h(R, \overline{Q})$

|    | S | Q | Q <sub>next</sub> |

|----|---|---|-------------------|

|    | 0 | 0 | 0                 |

| 1. | 0 | 1 | 1                 |

|    | 1 | 0 | 1                 |

|    | 1 | 1 | 1                 |

2.

$$Q_{next} = S + Q$$

3.

$$\overline{Q_{next}} = \overline{S+Q}$$

|    | R | $\overline{Q}$ | Q <sub>next</sub> |

|----|---|----------------|-------------------|

|    | 0 | 0              | 1                 |

| 4. | 0 | 1              | 0                 |

|    | 1 | 0              | 0                 |

|    | 1 | 1              | 0                 |

#### Flip-flop (or latch)

A flip-flop is a circuit that has two stables states. It can be used to store information.

#### Exercise

- 1. Write the truth table  $Q_{next} = f(S, Q)$

- 2. Deduce the logical function  $Q_{next} = f(S, Q)$

- 3. Write the logical function  $\overline{Q_{next}} = g(S, Q)$

- 4. Write the truth table  $Q_{next} = h(R, \overline{Q})$

- 5. Deduce the logical function  $Q_{next} = h(R, \overline{Q})$

|    | S | Q | Q <sub>next</sub> |

|----|---|---|-------------------|

|    | 0 | 0 | 0                 |

| 1. | 0 | 1 | 1                 |

|    | 1 | 0 | 1                 |

|    | 1 | 1 | 1                 |

2.

$$Q_{next} = S + Q$$

3.

$$\overline{Q_{next}} = \overline{S+Q}$$

5.

$$Q_{next} = R + \overline{Q}$$

#### Flip-flop (or latch)

A flip-flop is a circuit that has two stables states. It can be used to store information.

#### Exercise

- 1. Write the truth table  $Q_{next} = f(S, Q)$

- 2. Deduce the logical function  $Q_{next} = f(S, Q)$

- 3. Write the logical function  $\overline{Q_{next}} = g(S, Q)$

- 4. Write the truth table  $Q_{next} = h(R, \overline{Q})$

- 5. Deduce the logical function  $Q_{next} = h(R, \overline{Q})$

- 6. Draw the full circuit

|    | S | Q | Q <sub>next</sub> |

|----|---|---|-------------------|

|    | 0 | 0 | 0                 |

| 1. | 0 | 1 | 1                 |

|    | 1 | 0 | 1                 |

|    | 1 | 1 | 1                 |

$$2. \quad Q_{next} = S + Q$$

3.

$$\overline{Q_{next}} = \overline{S+Q}$$

5.

$$Q_{next} = R + \overline{Q}$$

#### Flip-flop (or latch)

A flip-flop is a circuit that has two stables states. It can be used to store information.

#### Exercise

- 1. Write the truth table  $Q_{next} = f(S, Q)$

- 2. Deduce the logical function  $Q_{next} = f(S, Q)$

- 3. Write the logical function  $\overline{Q_{next}} = g(S, Q)$

- 4. Write the truth table  $Q_{next} = h(R, \overline{Q})$

- 5. Deduce the logical function  $Q_{next} = h(R, \overline{Q})$

- 6. Draw the full circuit

|    | S | Q | Q <sub>next</sub> |

|----|---|---|-------------------|

|    | 0 | 0 | 0                 |

| 1. | 0 | 1 | 1                 |

|    | 1 | 0 | 1                 |

|    | 1 | 1 | 1                 |

2.

$$Q_{next} = S + Q$$

3.

$$\overline{Q_{next}} = \overline{S+Q}$$

5.

$$Q_{next} = R + \overline{Q}$$

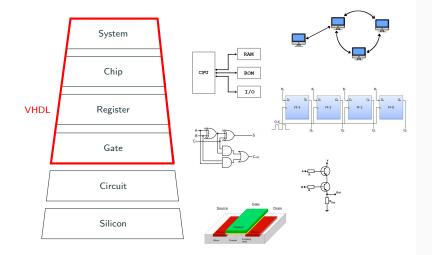

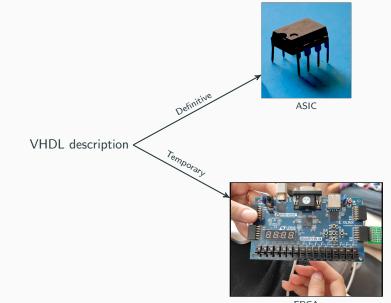

Introduction

• *Hardware Description Language*: describes the *behavior* of the system from which the physical circuit can then be implemented.

- *Hardware Description Language*: describes the *behavior* of the system from which the physical circuit can then be implemented.

- VHDL = "VHSIC Hardware Description Language". VHSIC = "Very High Speed Integrated Circuits".

- *Hardware Description Language*: describes the *behavior* of the system from which the physical circuit can then be implemented.

- VHDL = "VHSIC Hardware Description Language". VHSIC = "Very High Speed Integrated Circuits".

- Created in the 1980s.

- *Hardware Description Language*: describes the *behavior* of the system from which the physical circuit can then be implemented.

- VHDL = "VHSIC Hardware Description Language". VHSIC = "Very High Speed Integrated Circuits".

- Created in the 1980s.

- Two main applications: *programmable logic devices* (CPLD, FPGA) and design of *integrated circuit* (ASIC)

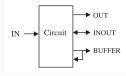

VHDL description

# About VHDL

# About VHDL

#### **EDA Tools**

• Electronic Design Automation tools: synthesis, implementation and simulation of VHDL.

#### **EDA Tools**

- Electronic Design Automation tools: synthesis, implementation and simulation of VHDL.

- Some tools are offered as part of vendor's design suite: Altera, Xilinx, ...

#### **EDA Tools**

- Electronic Design Automation tools: synthesis, implementation and simulation of VHDL.

- Some tools are offered as part of vendor's design suite: Altera, Xilinx, ...

- During this course we will use Xilinx's Vivado suite, for Xilinx's CPLD/FPGA chips

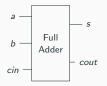

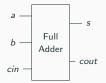

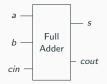

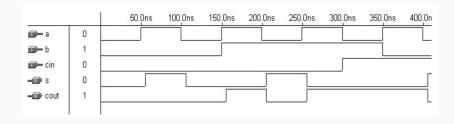

| а | b | cin | 5 | cout |

|---|---|-----|---|------|

| 0 | 0 | 0   | 0 | 0    |

| 0 | 1 | 0   | 1 | 0    |

| 1 | 0 | 0   | 1 | 0    |

| 1 | 1 | 0   | 0 | 1    |

| 0 | 0 | 1   | 1 | 0    |

| 0 | 1 | 1   | 0 | 1    |

| 1 | 0 | 1   | 0 | 1    |

| 1 | 1 | 1   | 1 | 1    |

|   | 1 | •   |   |      |

|---|---|-----|---|------|

| а | b | cin | S | cout |

| 0 | 0 | 0   | 0 | 0    |

| 0 | 1 | 0   | 1 | 0    |

| 1 | 0 | 0   | 1 | 0    |

| 1 | 1 | 0   | 0 | 1    |

| 0 | 0 | 1   | 1 | 0    |

| 0 | 1 | 1   | 0 | 1    |

| 1 | 0 | 1   | 0 | 1    |

| 1 | 1 | 1   | 1 | 1    |

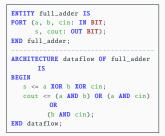

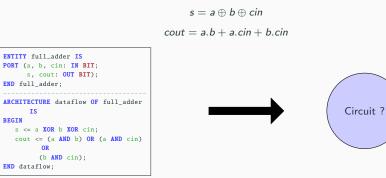

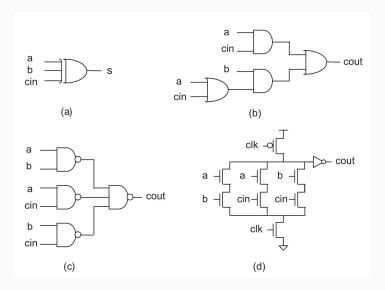

$s = a \oplus b \oplus cin$

| а | b | cin | 5 | cout |

|---|---|-----|---|------|

| 0 | 0 | 0   | 0 | 0    |

| 0 | 1 | 0   | 1 | 0    |

| 1 | 0 | 0   | 1 | 0    |

| 1 | 1 | 0   | 0 | 1    |

| 0 | 0 | 1   | 1 | 0    |

| 0 | 1 | 1   | 0 | 1    |

| 1 | 0 | 1   | 0 | 1    |

| 1 | 1 | 1   | 1 | 1    |

$s = a \oplus b \oplus cin$

cout = a.b + a.cin + b.cin

$s = a \oplus b \oplus cin$

$$cout = a.b + a.cin + b.cin$$

IS BEGIN

# Translation of VHDL Code into a Circuit

- Adders

- Counters

- Comparators

- ALU

- MAC unit

- Decoder/Encoder

- RAM, ROM

- Digital filters

- State machine

- Microprocessor

- Neural network

- ...

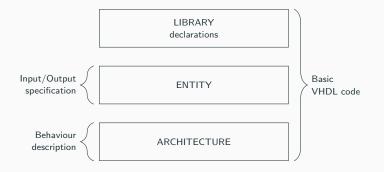

**Code structure**

LIBRARY library\_name;

USE library\_name.package\_name.package\_parts;

| LIBRA | ARY        |

|-------|------------|

| I     | PACKAGE    |

|       | FUNCTIONS  |

|       | PROCEDURES |

|       | COMPONENTS |

|       | CONSTANTS  |

|       | TYPES      |

|       |            |

Three packages are usually needed in a design:

```

LIBRARY ieee; -- A semi-colon (;) indicates

USE ieee.std_logic_1164.all; -- the end of a statement or

LIBRARY std; -- declaration, while a double

USE std.standard.all; -- dash (--) indicates a comment.

LIBRARY work;

USE work.all;

```

Three packages are usually needed in a design:

```

LIBRARY ieee; -- A semi-colon (;) indicates

USE ieee.std_logic_1164.all; -- the end of a statement or

LIBRARY std; -- declaration, while a double

USE std.standard.all; -- dash (--) indicates a comment.

LIBRARY work;

USE work.all;

```

Their purposes:

- ieee.std\_logic\_1164: specifies the STD\_LOGIC and STD\_ULOGIC datatypes;

- std: resource library for the VHDL design environment (loaded by default);

- work: current working library (loaded by default).

# An ENTITY is a list with specifications of all input and output pins (PORT) of the circuit.

An ENTITY is a list with specifications of all input and output pins (PORT) of the circuit.

```

ENTITY entity_name IS

PORT (

port_name : signal_mode signal_type;

port_name : signal_mode signal_type;

...);

END entity_name;

```

An ENTITY is a list with specifications of all input and output pins (PORT) of the circuit.

| ENTITY nand_gate IS<br>PORT (a, b : IN BIT: |

|---------------------------------------------|

| s : OUT BIT);                               |

| <pre>END nand_gate;</pre>                   |

ARCHITECTURE architecture\_name OF entity\_name IS

[declarations]

BEGIN

(code)

END architecture\_name;

```

ARCHITECTURE architecture_name OF entity_name IS

[declarations]

BEGIN

(code)

END architecture_name;

```

declarative part: where signals and constants (among others) are declared

```

ARCHITECTURE architecture_name OF entity_name IS

[declarations]

BEGIN

(code)

END architecture_name;

```

- *declarative* part: where signals and constants (among others) are declared

- code part: behaviour is described

```

ARCHITECTURE architecture_name OF entity_name IS

[declarations]

BEGIN

(code)

END architecture_name;

```

- *declarative* part: where signals and constants (among others) are declared

- code part: behaviour is described

```

ARCHITECTURE myarch OF nand_gate IS

BEGIN

s <= a NAND b;

END myarch;

```

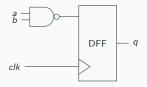

```

ENTITY example IS

PORT (a, b, clk: IN BIT;

q: OUT BIT);

END example;

ARCHITECTURE example OF example IS

SIGNAL temp : BIT;

BEGIN

temp <= a NAND b;

PROCESS (clk)

BEGIN

IF (clk'EVENT AND clk='1') THEN q<=temp;

END PROCESS;

END PROCESS;

END example;

```

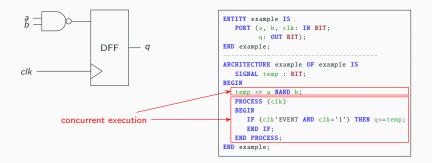

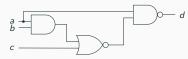

Write the VHDL code of the following circuit:

There are 3 inputs, and 1 output, and 2 internal signals (optionals). You will only use **BIT** datatype. You will need to use some of the logical operators: **AND, OR, NAND, NOR, XOR**. Write the VHDL code of the following circuit:

There are 3 inputs, and 1 output, and 2 internal signals (optionals).

You will only use **BIT** datatype. You will need to use some of the logical operators: **AND, OR, NAND, NOR, XOR**.

```

ENTITY example IS

PORT (a, b, c: IN BIT;

d: OUT BIT);

END example;

ARCHITECTURE my_example OF example IS

SIGNAL tmp1 : BIT;

SIGNAL tmp2 : BIT;

BEGIN

tmp1 <= a AND b;

tmp2 <= tmp1 NOR c;

d <= a NAND tmp2;

END my_example;

```

```

ENTITY example2 IS

PORT (a, b, c: IN BIT;

d: OUT BIT);

END example2;

ARCHITECTURE my_example2 OF example2 IS

BEGIN

d <= ((a AND b) NOR c ) NAND a;

END my_example2;

```

# VHDL

Data types

• std.standard: Defines BIT, BOOLEAN, INTEGER, and REAL data types;

- std.standard: Defines BIT, BOOLEAN, INTEGER, and REAL data types;

- ieee.std\_logic\_1164: Defines **STD\_LOGIC** and **STD\_ULOGIC** data types;

- std.standard: Defines BIT, BOOLEAN, INTEGER, and REAL data types;

- ieee.std\_logic\_1164: Defines STD\_LOGIC and STD\_ULOGIC data types;

- ieee.numeric\_std: Defines SIGNED and UNSIGNED data types, plus several data conversion functions, like to\_integer(p), to\_unsigned(p,b), to\_signed(p,b);

- std.standard: Defines BIT, BOOLEAN, INTEGER, and REAL data types;

- ieee.std\_logic\_1164: Defines STD\_LOGIC and STD\_ULOGIC data types;

- ieee.numeric\_std: Defines SIGNED and UNSIGNED data types, plus several data conversion functions, like to\_integer(p), to\_unsigned(p,b), to\_signed(p,b);

- ieee.std\_logic\_signed and ieee.std\_logic\_unsigned: Contain functions that allow operations with STD\_LOGIC\_VECTOR data to be performed as if the data were of type SIGNED or UNSIGNED, respectively.

Definition BIT (and BIT\_VECTOR): 2-level logic ('0', '1').

## Definition

```

BIT (and BIT_VECTOR): 2-level logic ('0', '1').

```

## Example

SIGNAL x: BIT; -- x is declared as a one-digit signal of type BIT. SIGNAL y: BIT\_VECTOR (3 DOWNTO 0); -- y is a 4-bit vector, with the leftmost bit being the MSB. SIGNAL w: BIT\_VECTOR (0 TO 7); -- w is an 8-bit vector, with the rightmost bit being the MSB.

```

x <= '1';

-- x is a single-bit signal (as specified above), whose value is '1'.

-- Notice that single quotes (' ') are used for a single bit.

y <= "0111";

-- y is a 4-bit signal (as specified above), whose value is "0111" (MSB='0').

-- Notice that double quotes (" ") are used for vectors.

w <= "01110001";

-- w is an 8-bit signal, whose value is "01110001" (MSB='1').

```

# STD\_LOGIC

# Definition

**STD\_LOGIC** (and **STD\_LOGIC\_VECTOR**): 8-valued logic system introduced in the IEEE 1164 standard.

- 'X' Forcing Unknown (synthesizable unknown)

- '0' Forcing Low (synthesizable logic '0')

- '1' Forcing High (synthesizable logic '1')

- 'Z' High impedance (synthesizable tri-state buffer)

- 'W' Weak unknown (can't tell if it should be 0 or 1)

- 'L' Weak low (that should pro

- 'H' Weak high (that

- '-' Don't care

(that should probably go to 0)

(that should probably go to 1)

# STD\_LOGIC

## Definition

**STD\_LOGIC** (and **STD\_LOGIC\_VECTOR**): 8-valued logic system introduced in the IEEE 1164 standard.

| ʻX' | Forcing Unknown | (synthesizable unknown)             |

|-----|-----------------|-------------------------------------|

| '0' | Forcing Low     | (synthesizable logic '0')           |

| '1' | Forcing High    | (synthesizable logic '1')           |

| 'Z' | High impedance  | (synthesizable tri-state buffer)    |

| 'W' | Weak unknown    | (can't tell if it should be 0 or 1) |

| ʻL' | Weak low        | (that should probably go to 0)      |

| 'Η' | Weak high       | (that should probably go to 1)      |

# Example

Don't care

٤\_,

```

SIGNAL x: STD_LOGIC;

-- x is declared as a one-digit (scalar) signal of type STD_LOGIC.

SIGNAL y: STD_LOGIC_VECTOR (3 DOWNTO 0) := "0001";

-- y is declared as a 4-bit vector, with the leftmost bit being the MSB.

-- The initial value (optional) of y is "0001".

-- Notice that the ":=" operator is used to establish the initial value.

```

# STD\_ULOGIC

## Definition

**STD\_ULOGIC** (and **STD\_ULOGIC\_VECTOR**): 9-level logic system introduced in the IEEE 1164 standard ('U', 'X', '0', '1', 'Z', 'W', 'L', 'H', '-').

'U' stands for  $Unresolved \implies$  Driver conflicts

# STD\_ULOGIC

## Definition

STD\_ULOGIC (and STD\_ULOGIC\_VECTOR): 9-level logic system introduced in the IEEE 1164 standard ('U', 'X', '0', '1', 'Z', 'W', 'L', 'H', '-').

'U' stands for  $Unresolved \implies$  Driver conflicts

**Resolved logic system**

|   | Х | 0 | 1 | Ζ | W | L | Н | - |

|---|---|---|---|---|---|---|---|---|

| Х | Х | Х | Х | Х | Х | Х | Х | Х |

| 0 | X | 0 | Х | 0 | 0 | 0 | 0 | Х |

| 1 | X | Х | 1 | 1 | 1 | 1 | 1 | Х |

| Z | X | 0 | 1 | Ζ | W | L | Η | Х |

| W | X | 0 | 1 | W | W | W | W | Х |

| L | X | 0 | 1 | L | W | L | W | Х |

| Н | X | 0 | 1 | Η | W | W | Η | Х |

| - | Х | Х | Х | Х | Х | Х | Х | Х |

#### INTEGER

32-bit integers (from -2,147,483,647 to +2,147,483,647).

### INTEGER

32-bit integers (from -2,147,483,647 to +2,147,483,647).

## NATURAL

Non-negative integers (from 0 to +2,147,483,647).

### INTEGER

32-bit integers (from -2,147,483,647 to +2,147,483,647).

## NATURAL

Non-negative integers (from 0 to +2,147,483,647).

#### REAL

Real numbers ranging from -1.0E38 to +1.0E38. Not synthesizable.

### INTEGER

32-bit integers (from -2,147,483,647 to +2,147,483,647).

## NATURAL

Non-negative integers (from 0 to +2,147,483,647).

#### REAL

Real numbers ranging from -1.0E38 to +1.0E38. Not synthesizable.

#### **Physical literals**

Used to inform physical quantities, like time, voltage, etc. Useful in simulations. Not synthesizable.

### INTEGER

32-bit integers (from -2,147,483,647 to +2,147,483,647).

## NATURAL

Non-negative integers (from 0 to +2,147,483,647).

#### REAL

Real numbers ranging from -1.0E38 to +1.0E38. Not synthesizable.

### **Physical literals**

Used to inform physical quantities, like time, voltage, etc. Useful in simulations. Not synthesizable.

#### **Character literals**

Single ASCII character or a string of such characters. Not synthesizable.

### INTEGER

32-bit integers (from -2,147,483,647 to +2,147,483,647).

## NATURAL

Non-negative integers (from 0 to +2,147,483,647).

#### REAL

Real numbers ranging from -1.0E38 to +1.0E38. Not synthesizable.

#### **Physical literals**

Used to inform physical quantities, like time, voltage, etc. Useful in simulations. Not synthesizable.

#### **Character literals**

Single ASCII character or a string of such characters. Not synthesizable.

### SIGNED and UNSIGNED

Data types defined in the ieee.numeric\_std package. They have the appearance of STD\_LOGIC\_VECTOR, but accept arithmetic operations, which are typical of INTEGER data types.

# High level Data Types

# Example

| x0 <= '0';          | bit, std_logic, or std_ulogic value '0'                              |

|---------------------|----------------------------------------------------------------------|

| x1 <= "000111111";  | bit_vector, std_logic_vector, std_ulogic_vector, signed, or unsigned |

| x2 <= "0001_11111"; | underscore allowed to ease visualization                             |

| x3 <= "101111";     | binary representation of decimal 47                                  |

| x4 <= B"101111";    | binary representation of decimal 47                                  |

| x5 <= 0"57";        | octal representation of decimal 47                                   |

| x6 <= X"2F";        | hexadecimal representation of decimal 47                             |

| n <= 1200;          | integer                                                              |

| m <= 1_200;         | integer, underscore allowed                                          |

| IF ready THEN       | Boolean, executed if ready=TRUE                                      |

| y <= 1.2E-5;        | real, not synthesizable                                              |

| q <= d AFTER 10 NS; | physical, not synthesizable                                          |

# High level Data Types

## Example

| x0 <= '0';          | bit, std_logic, or std_ulogic value '0'                              |

|---------------------|----------------------------------------------------------------------|

| x1 <= "000111111";  | bit_vector, std_logic_vector, std_ulogic_vector, signed, or unsigned |

| x2 <= "0001_1111";  | underscore allowed to ease visualization                             |

| x3 <= "1011111";    | binary representation of decimal 47                                  |

| x4 <= B"101111";    | binary representation of decimal 47                                  |

| x5 <= 0"57";        | octal representation of decimal 47                                   |

| x6 <= X"2F";        | hexadecimal representation of decimal 47                             |

| n <= 1200;          | integer                                                              |

| m <= 1_200;         | integer, underscore allowed                                          |

| IF ready THEN       | Boolean, executed if ready=TRUE                                      |

| y <= 1.2E-5;        | real, not synthesizable                                              |

| q <= d AFTER 10 NS; | physical, not synthesizable                                          |

|                     |                                                                      |

#### Example

Operations between data of differents types:

#### Integer

| TYPE integer IS RANGE -2147483647 TO +2147483647; | This is indeed the pre-defined type INTEGER.   |

|---------------------------------------------------|------------------------------------------------|

| TYPE natural IS RANGE 0 TO +2147483647;           | This is indeed the pre-defined type NATURAL.   |

| TYPE my_integer IS RANGE -32 TO 32;               | A user-defined subset of integers.             |

| TYPE student_grade IS RANGE 0 TO 100;             | A user-defined subset of integers or naturals. |

#### Integer

| TYPE integer IS RANGE -2147483647 TO +2147483647; | This is indeed the pre-defined type INTEGER.   |

|---------------------------------------------------|------------------------------------------------|

| TYPE natural IS RANGE 0 TO +2147483647;           | This is indeed the pre-defined type NATURAL.   |

| TYPE my_integer IS RANGE -32 TO 32;               | A user-defined subset of integers.             |

| TYPE student_grade IS RANGE 0 TO 100;             | A user-defined subset of integers or naturals. |

#### Enumerated

| TYPE bit IS ('0', '1');                             | This is indeed the pre-defined type BIT          |

|-----------------------------------------------------|--------------------------------------------------|

| TYPE my_logic IS ('0', '1', 'Z');                   | A user-defined subset of std_logic.              |

| TYPE bit_vector IS ARRAY (NATURAL RANGE <>) OF BIT; | This is indeed the pre-defined type BIT_VECTOR.  |

|                                                     | RANGE <> is used to indicate that the range is   |

|                                                     | unconstrained.                                   |

|                                                     | NATURAL RANGE <>, on the other hand, indicates   |

|                                                     | that the only restriction is that the range must |

|                                                     | fall within the NATURAL range.                   |

| TYPE state IS (idle, forward, backward, stop);      | An enumerated data type,                         |

|                                                     | typical of finite state machines.                |

| TYPE color IS (red, green, blue, white);            | Another enumerated data type.                    |

|                                                     |                                                  |

```

SIGNAL x: SIGNED (7 DOWNTO 0);

SIGNAL y: UNSIGNED (0 TO 3);

```

### Example

```

SIGNAL x: SIGNED (7 DOWNTO 0);

SIGNAL y: UNSIGNED (0 TO 3);

```

Similar to STD\_LOGIC\_VECTOR, and not like INTEGER

#### Example

```

SIGNAL x: SIGNED (7 DOWNTO 0);

SIGNAL y: UNSIGNED (0 TO 3);

```

Similar to STD\_LOGIC\_VECTOR, and not like INTEGER

For arithmetic operations purpose

#### Example

```

SIGNAL x: SIGNED (7 DOWNTO 0);

SIGNAL y: UNSIGNED (0 TO 3);

```

#### Similar to STD\_LOGIC\_VECTOR, and not like INTEGER

For arithmetic operations purpose

```

LIRRAFY ieee;

USE ieee.std_logic_l164.all;

USE ieee.numeric_std.all;

-- extra package necessary

...

SIGNAL a: SIGNED (7 DOWNTO 0);

SIGNAL v: SIGNED (7 DOWNTO 0);

SIGNAL v: SIGNED (7 DOWNTO 0);

...

v <= a + b; --legal (arithmetic operation OK)

w <= a AND b; --illegal (logical operation not OK)

```

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

-- no extra package required

...

SIGNAL a: STD_LOGIC_VECTOR (7 DOWNTO 0);

SIGNAL b: STD_LOGIC_VECTOR (7 DOWNTO 0);

SIGNAL v: STD_LOGIC_VECTOR (7 DOWNTO 0);

...

v <= a + b; --illegal (arithmetic operation not OK)

w <= a AND b; --legal (logical operation OK)

```

# SIGNED and UNSIGNED

From the package ieee.numeric\_std

#### Example

```

SIGNAL x: SIGNED (7 DOWNTO 0);

SIGNAL y: UNSIGNED (0 TO 3);

```

Similar to STD\_LOGIC\_VECTOR, and not like INTEGER

For arithmetic operations purpose

```

LIRRARY ieee

LIBRARY ieee:

USE ieee.std logic 1164.all:

USE ieee.std_logic_1164.all;

USE ieee.numeric std.all:

-- no extra package required

-- extra package necessary

SIGNAL a: STD LOGIC VECTOR (7 DOWNTO 0):

SIGNAL a: SIGNED (7 DOWNTO 0):

SIGNAL b: STD_LOGIC_VECTOR (7 DOWNTO 0);

SIGNAL b: SIGNED (7 DOWNTO 0):

SIGNAL v: STD_LOGIC_VECTOR (7 DOWNTO 0);

SIGNAL v: SIGNED (7 DOWNTO 0):

SIGNAL w: STD_LOGIC_VECTOR (7 DOWNTO 0);

SIGNAL w: SIGNED (7 DOWNTO 0):

v <= a + b: --illegal (arithmetic operation not OK)</pre>

v <= a + b; --legal (arithmetic operation OK)</pre>

w <= a AND b: --legal (logical operation OK)

w <= a AND b; --illegal (logical operation not OK)</pre>

```

Possible to use packages std\_logic\_signed and std\_logic\_unsigned (from the ieee library) to do arithmetic operations on STD\_LOGIC\_VECTOR.

| ĺ | function                          | type of p                 | b           |

|---|-----------------------------------|---------------------------|-------------|

| [ | <pre>to_integer(p)</pre>          | INTEGER, UNSIGNED, SIGNED |             |

|   | to_unsigned(p,b)                  | INTEGER                   | size (bits) |

|   | <pre>to_signed(p,b)</pre>         | INTEGER                   | size (bits) |

|   | <pre>signed(p)(*)</pre>           | STD_LOGIC_VECTOR          |             |

|   | unsigned(p)(*)                    | STD_LOGIC_VECTOR          |             |

|   | <pre>std_logic_vector(p)(*)</pre> | SIGNED, UNSIGNED          |             |

Several data conversion functions and type-casting in ieee.numeric\_std:

| function                          | type of p                 | b           |

|-----------------------------------|---------------------------|-------------|

| <pre>to_integer(p)</pre>          | INTEGER, UNSIGNED, SIGNED |             |

| <pre>to_unsigned(p,b)</pre>       | INTEGER                   | size (bits) |

| <pre>to_signed(p,b)</pre>         | INTEGER                   | size (bits) |

| signed(p)(*)                      | STD_LOGIC_VECTOR          |             |

| unsigned(p)(*)                    | STD_LOGIC_VECTOR          |             |

| <pre>std_logic_vector(p)(*)</pre> | SIGNED, UNSIGNED          |             |

Several data conversion functions and type-casting in ieee.numeric\_std:

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.numeric_std.all;

...

SIGNAL a: UNSIGNED (7 DOWNTO 0);

SIGNAL y: STD_LOGIC_VECTOR (7 DOWNTO 0);

...

y <= STD_LOGIC_VECTOR ((a+b), 8);

-- Legal operation: a+b is converted from UNSIGNED to an 8-bit STD_LOGIC_VECTOR value,

-- then assigned to y.

```

# VHDL

Operators

- Assignment operators

- Logical operators

- Arithmetic operators

- Relational operators

- Shift operators

- Concatenation operators

| <= | Used to assign a value to a <b>SIGNAL</b> .                         |

|----|---------------------------------------------------------------------|

| := | Used to assign a value to a VARIABLE, CONSTANT, or GENERIC.         |

|    | Used also for establishing initial values.                          |

| => | Used to assign values to individual vector elements or with OTHERS. |

| <= | Used to assign a value to a <b>SIGNAL</b> .                         |  |  |

|----|---------------------------------------------------------------------|--|--|

| := | Used to assign a value to a VARIABLE, CONSTANT, or GENERIC.         |  |  |

|    | Used also for establishing initial values.                          |  |  |

| => | Used to assign values to individual vector elements or with OTHERS. |  |  |

```

SIGNAL x : STD_LOGIC;

VARIABLE y : STD_LOGIC_VECTOR(3 DOWNTO 0); -- Leftmost bit is MSB

SIGNAL w: STD_LOGIC_VECTOR(0 TO 7); -- Rightmost bit is

...

x <= '1'; -- '1' is assigned to SIGNAL x using "<="

y := "06000"; -- "0000" is assigned to VARIABLE y using ":="

w <= "18000900"; -- LSB is '1', the others are '0'

w <= (0 =>'1', OTHERS =>'0'); -- LSB is '1', the others are '0'

```

NOT AND OR NAND NOR XOR XNOR

The data must be of type **BIT**, **STD\_LOGIC**, or **STD\_ULOGIC** (or, their respective extensions, **BIT\_VECTOR**, **STD\_LOGIC\_VECTOR**, or **STD\_ULOGIC\_VECTOR**).

NOT AND OR NAND NOR XOR XNOR

The data must be of type **BIT**, **STD\_LOGIC**, or **STD\_ULOGIC** (or, their respective extensions, **BIT\_VECTOR**, **STD\_LOGIC\_VECTOR**, or **STD\_ULOGIC\_VECTOR**).

```

y <= NOT a AND b;

y <= NOT (a AND b);

y <= a NAND b;

```

- + Addition

- Subtraction

- Multiplication

- / Division

- \*\* Exponentiation

- MODModulusREMRemainder

- ABS Absolute value

The data can be of type INTEGER, SIGNED, UNSIGNED, or REAL.

Also, if the std\_logic\_signed or the std\_logic\_unsigned package of the ieee library is used, then STD\_LOGIC\_VECTOR can also be employed directly in addition and subtraction operations.

| + Addition |  |

|------------|--|

|            |  |

- Subtraction

- Multiplication

- / Division

- \*\* Exponentiation

- MOD Modulus

- REM Remainder

- ABS Absolute value

The data can be of type INTEGER, SIGNED, UNSIGNED, or REAL.

Also, if the std\_logic\_signed or the std\_logic\_unsigned package of the ieee library is used, then STD\_LOGIC\_VECTOR can also be employed directly in addition and subtraction operations.

#### Warning

Must be carefull about the last five, the synthesis (if it is possible) may not be what you expect !

- = Equal to

- /= Not equal to

- < Less than

- > Greater than

- <= Less than or equal to

- >= Greater than or equal to

The data can be of any type listed above.

sllShift left logicpositions on the right are filled with '0'ssrlShift right logicpositions on the left are filled with '0's

The left operand must be of type **BIT\_VECTOR**, while the right operand must be an **INTEGER**.

sllShift left logicpositions on the right are filled with '0'ssrlShift right logicpositions on the left are filled with '0's

The left operand must be of type **BIT\_VECTOR**, while the right operand must be an **INTEGER**.

```

SIGNAL b : BIT_VECTOR (3 DOWNTO 0) := "1100";

SIGNAL x : BIT_VECTOR (3 DOWNTO 0);

SIGNAL y : BIT_VECTOR (3 DOWNTO 0);

...

x <= b sll 2; --- x <= "0000"

y <= b srl 1; --- y <= "0110"

```

The concatenation operator is denoted &.

The data can be of type BIT, STD\_LOGIC, or STD\_ULOGIC (or, their respective extensions, BIT\_VECTOR, STD\_LOGIC\_VECTOR, or STD\_ULOGIC\_VECTOR).

The concatenation operator is denoted &.

The data can be of type **BIT**, **STD\_LOGIC**, or **STD\_ULOGIC** (or, their respective extensions, **BIT\_VECTOR**, **STD\_LOGIC\_VECTOR**, or **STD\_ULOGIC\_VECTOR**).

```

SIGNAL a : BIT_VECTOR (3 DOWNTO 0) := "1001";

SIGNAL b : BIT_VECTOR (3 DOWNTO 0) := "1100";

SIGNAL x : BIT_VECTOR (7 DOWNTO 0);

...

x <= a & b; -- x <= "10011100"</pre>

```

Their syntax is the following: signal\_name'attribute\_name

| s'EVENT       | Returns true when an event occurs on s       |

|---------------|----------------------------------------------|

| s'STABLE      | Returns true if no event has occurred on s   |

| s'ACTIVE      | Returns true if s='1'                        |

| s'LAST_EVENT  | Returns the time elapsed since last event    |

| s'LAST_ACTIVE | Returns the time elapsed since last s='1'    |

| s'LAST_VALUE  | Returns the value of s before the last event |

Their syntax is the following: signal\_name'attribute\_name

| s'EVENT       | Returns true when an event occurs on s       |

|---------------|----------------------------------------------|

| s'STABLE      | Returns true if no event has occurred on s   |

| s'ACTIVE      | Returns true if s='1'                        |

| s'LAST_EVENT  | Returns the time elapsed since last event    |

| s'LAST_ACTIVE | Returns the time elapsed since last s='1'    |

| s'LAST_VALUE  | Returns the value of s before the last event |

```

IF (clk'EVENT AND clk='1')... -- EVENT attribute used with IF

IF (NOT clk'STABLE AND clk='1')... - STABLE attribute used with IF

WAIT UNTLI (clk'EVENT AND clk='1'); -- EVENT attribute used with wait

```

• There exists more operators (sla, sra, rol, ...);

- There exists more operators (sla, sra, rol, ...);

- There exists more attributes (LOW, HIGH, LEFT, ...);

- There exists more operators (sla, sra, rol, ...);

- There exists more attributes (LOW, HIGH, LEFT, ...);

- You can define your own attribute;

- There exists more operators (sla, sra, rol, ...);

- There exists more attributes (LOW, HIGH, LEFT, ...);

- You can define your own attribute;

- You can overload the existing operators.

## Exercise

Determine the values of the xi and d.

```

SIGNAL a : BIT := '1';

SIGNAL b : BIT_VECTOR (3 DOWNTO 0) := "1000";

SIGNAL c : BIT_VECTOR (7 DOWNTO 0);

...

x1 <= a & c;

x2 <= c & b;

x3 <= b XOR c;

x4 <= a NOR b(3);

x5 <= b SIl 2;

x6 <= b SIl 2;

x7 <= a AND NOT b(0) AND NOT c(1);

d <= (5=>'0', OTHERS=>'1');

```

## Exercise

Determine the values of the xi and d.

```

SIGNAL a : BIT := '1';

SIGNAL b : BIT_VECTOR (3 DOWNTO 0) := "1100";

SIGNAL c : BIT_VECTOR (7 DOWNTO 0);

...

x1 <= a & c;

x2 <= c & b;

x3 <= b XOR c;

x4 <= a NOR b(3);

x5 <= b SIl 2;

x6 <= b SIl 2;

x7 <= a AND NOT b(0) AND NOT c(1);

d <= (5=>'0', OTHERS=>'1');

```

### Solution

```

x1 <= "10010";

x2 <= "00101100";

x3 <= "1110";

x4 <= '0';

x5 <= "0000";

x6 <= "0110";

x7 <= '0';

d <= "11011111";</pre>

```

# VHDL

Concurrent code

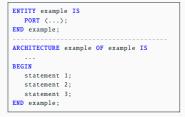

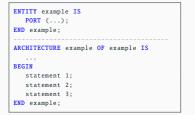

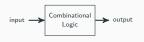

VHDL code is inherently *concurrent* (parallel).

VHDL code is inherently *concurrent* (parallel).

The order of the statements does not matter.

$\equiv$

| ENTITY exampl<br>PORT ()<br>END example; |         |    |         |    |

|------------------------------------------|---------|----|---------|----|

| ARCHITECTURE                             | example | OF | example | IS |

| BEGIN                                    |         |    |         |    |

| statement                                | '       |    |         |    |

| statement                                | 3;      |    |         |    |

| statement                                | 1;      |    |         |    |

| <pre>END example;</pre>                  |         |    |         |    |

# **Concurrent code**

VHDL code is inherently *concurrent* (parallel).

The order of the statements does not matter.

=

Perfect to build combinatonial logic circuits.

| ENTITY exampl<br>PORT ()<br>END example; |         |    |         |    |

|------------------------------------------|---------|----|---------|----|

| ARCHITECTURE                             | example | OF | example | IS |

|                                          |         |    |         |    |

| BEGIN                                    |         |    |         |    |

| statement                                | 2;      |    |         |    |

| statement                                | 3;      |    |         |    |

| statement                                | 1;      |    |         |    |

| <pre>END example;</pre>                  |         |    |         |    |

# Concurrent code

VHDL code is inherently concurrent (parallel).

The order of the statements does not matter.

| <pre>ENTITY example IS     PORT (); END example;</pre> |              |

|--------------------------------------------------------|--------------|

| ARCHITECTURE example 0                                 | F example IS |

| BEGIN                                                  |              |

| statement 2;                                           |              |

| statement 3;                                           |              |

| statement 1;                                           |              |

| <pre>END example;</pre>                                |              |

Perfect to build combinatonial logic circuits.

#### **Concurrents statements**

- Operators;

- The WHEN statement (WHEN/ELSE or WITH/SELECT/WHEN);

=

- The **GENERATE** statement;

- The **BLOCK** statement.

It is the *conditional* concurrent statement.

It is the *conditional* concurrent statement.

It appears in two forms:

### WHEN/ELSE (simple WHEN)

assignment WHEN condition ELSE assignment WHEN condition ELSE ...;

### WITH/SELECT/WHEN (selected WHEN)

WITH identifier SELECT assignment WHEN value, assignment WHEN value, ...;

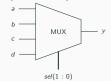

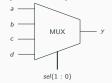

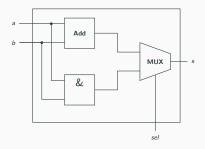

# WHEN statement

**Example** An example of Multiplexer

| sel | У |

|-----|---|

| 00  | а |

| 01  | Ь |

| 10  | с |

| 11  | d |

### WHEN statement

#### Example

An example of Multiplexer

```

----- Solution 2: with WITH/SELECT/WHEN ------

LIBRARY ieee:

USE ieee.std logic 1164.all:

ENTITY mux IS

PORT ( a, b, c, d: IN STD_LOGIC;

sel: IN STD_LOGIC_VECTOR (1 DOWNTO 0);

v: OUT STD LOGIC):

END mux:

ARCHITECTURE mux2 OF mux IS

BEGIN

WITH sel SELECT

v <= a WHEN "00".-- notice "." instead of ":"</pre>

b WHEN "01".

C WHEN "10".

d WHEN OTHERS: -- cannot be "d WHEN "11"

END mux2;

```

# **GENERATE** statement

It is the loop concurrent statement.

### FOR/GENERATE

```

label: FOR identifier IN range GENERATE

(concurrent assignments)

END GENERATE;

```

# **GENERATE** statement

It is the loop concurrent statement.

#### FOR/GENERATE

```

label: FOR identifier IN range GENERATE

(concurrent assignments)

END GENERATE;

```

#### Example

```

SIGNAL x: BIT_VECTOR (7 DOWNTO 0);

SIGNAL y: BIT_VECTOR (15 DOWNTO 0);

SIGNAL z: BIT_VECTOR (15 DOWNTO 0);

...

G1: FOR i IN x'RANGE GENERATE

z(i) <= x(i) AND y(i+8);

END GENERATE;

G2: FOR i IN 0 TO 7 GENERATE

z(i+8) <= x(i) OR y(i);

END GENERATE;

```

## **GENERATE** statement

It is the loop concurrent statement.

#### FOR/GENERATE

```

label: FOR identifier IN range GENERATE

(concurrent assignments)

END GENERATE;

```

#### Example

```

SIGNAL x: BIT_VECTOR (7 DOWNTO 0);

SIGNAL y: BIT_VECTOR (15 DOWNTO 0);

SIGNAL z: BIT_VECTOR (15 DOWNTO 0);

...

G1: FOR i IN x'RANGE GENERATE

z(i) <= x(i) AND y(i+8);

END GENERATE;

G2: FOR i IN 0 TO 7 GENERATE

z(i+8) <= x(i) OR y(i);

END GENERATE;

```

#### Warning

- Limits of the range must be static;

- No multiply-driven signals allowed.

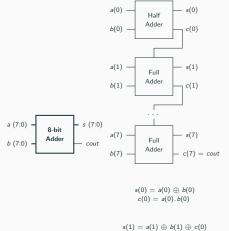

$\begin{array}{l} s(0) = a(0) \oplus b(0) \\ c(0) = a(0) \cdot b(0) \end{array}$

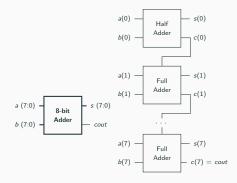

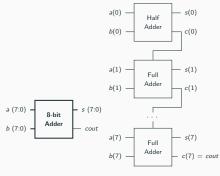

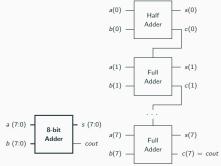

### Exercise

Build an 8-bit Adder using only logical operations.

$s(0) = a(0) \oplus b(0)$  $c(0) = a(0) \cdot b(0)$

$$s(1) = a(1) \oplus b(1) \oplus c(0)$$

$$c(1) = a(1).b(1) + a(1).c(0) + b(1).c(0)$$

### Exercise

Build an 8-bit Adder using only logical operations.

$c(1) = a(1) \cdot b(1) + a(1) \cdot c(0) + b(1) \cdot c(0)$

```

ENTITY adder 8 bits IS

PORT (a, b: IN STD_LOGIC_VECTOR (7 DOWNTO 0);

s: OUT STD_LOGIC_VECTOR (7 DOWNTO 0);

cout: OUT STD_LOGIC);

END adder_8_bits;

ARCHITECTURE my adder OF adder 8 bits IS

SIGNAL c : STD_LOGIC_VECTOR (7 DOWNTO 0);

SIGNAL i : INTEGER RANGE 0 TO 7;

BEGIN

-- Half Adder on bit 0

s(0) <= a(0) XOR b(0);

c(0) \le a(0) AND b(0):

-- Generate all the Full Adders

G1: FOR i IN 1 TO 7 GENERATE

-- Full Adder on bit i

s(i) <= a(i) XOR b(i) XOR c(i-1);</pre>

c(i) <= (a(i) AND b(i)) OR (a(i) AND c(i-1))

OR (b(i) AND c(i-1));

END GENERATE:

-- Last carry is cout

cout <= c(7);

```

END my\_adder;

# VHDL

Sequential code

In sequential code, the statements are executed in order.

In sequential code, the statements are executed in order.

In VHDL, the only code executed *sequentially* is in the sections **PROCESS**, **FUNCTION**, or **PROCEDURE**.

# PROCESS

The section **PROCESS** has the following syntax:

```

[label:] PROCESS (sensitivity list)

[VARIABLE name type [range] [:= initial_value;]]

BEGIN

(sequential code)

END PROCESS [label];

```

# PROCESS

The section **PROCESS** has the following syntax:

```

[label:] PROCESS (sensitivity list)

[VARIABLE name type [range] [:= initial_value;]]

BEGIN

(sequential code)

END PROCESS [label];

```

#### VARIABLE

VARIABLE are the equivalent of SIGNAL for a PROCESS. But there are some difference:

- They can only be used inside a PROCESS, FUNCTION, or PROCEDURE;

- They are defined locally;

- The assignement operator is := .

# PROCESS

The section **PROCESS** has the following syntax:

```

[label:] PROCESS (sensitivity list)

[VARIABLE name type [range] [:= initial_value;]]

BEGIN

(sequential code)

END PROCESS [label];

```

#### VARIABLE

VARIABLE are the equivalent of SIGNAL for a PROCESS. But there are some difference:

- They can only be used inside a PROCESS, FUNCTION, or PROCEDURE;

- They are defined locally;

- The assignement operator is := .

#### Sequential statements

- The IF statement;

- The WAIT statement;

- The CASE statement;

- The LOOP statement.

It is a *conditional* sequential statement.

IF conditions THEN assignments; ELSIF conditions THEN assignments; ... ELSE assignments; END IF; It is a *conditional* sequential statement.

```

IF conditions THEN assignments;

ELSIF conditions THEN assignments;

...

ELSE assignments;

END IF;

```

#### Example

```

IF (x<y) THEN temp:="111111111";

ELSIF (x=y AND w='0') THEN temp:="11110000";

ELSE temp:=(OTHERS =>'0');

```

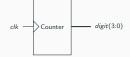

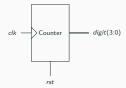

#### Example A 1-digit counter (from 0 to 9)

#### **Example** A 1-digit counter (from 0 to 9)

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY counter IS

PORT (clk : IN STD_LOGIC;

digit : OUT INTEGER RANGE 0 TO 9);

END counter;

ARCHITECTURE counter OF counter IS

REGIN

count: PROCESS(clk)

VARIABLE temp : INTEGER RANGE 0 TO 10;

BEGIN

IF (clk'EVENT AND clk='1') THEN

temp := temp + 1:

IF (temp=10) THEN temp := 0;

END IF:

END IF;

digit <= temp;

END PROCESS count;

END counter:

```

#### Example A 1-digit counter (from 0 to 9)

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY counter IS

PORT (clk : IN STD_LOGIC;

digit : OUT INTEGER RANGE 0 TO 9);

END counter;

ARCHITECTURE counter OF counter IS

REGIN

count: PROCESS(clk)

VARIABLE temp : INTEGER RANGE 0 TO 10;

BEGIN

IF (clk'EVENT AND clk='1') THEN

temp := temp + 1:

IF (temp=10) THEN temp := 0;

END IF:

END IF;

digit <= temp;

END PROCESS count;

END counter:

```

#### Result

|                |         | [      | 100.0ns | 200.0ns | 300.0ns   | 400.0ns |

|----------------|---------|--------|---------|---------|-----------|---------|

| n clk<br>digit | 0<br>H0 | 0)(1)( | 2)3     |         | 6 ( 7 ) 8 | (9)0)1  |

```

CASE identifier IS

WHEN value => assignments;

WHEN value => assignments;

...

END CASE;

```

```

CASE identifier IS

WHEN value => assignments;

WHEN value => assignments;

...

END CASE;

```

#### Example

```

CASE control IS

WHEN "00" => x<=a; y<=b;

WHEN "01" => x<=b; y<=c;

WHEN OTHERS => x<="0000"; y<="ZZZZ";

END CASE;

```

```

CASE identifier IS

WHEN value => assignments;

WHEN value => assignments;

...

END CASE;

```

#### Example

```

CASE control IS

WHEN "00" => x<=a; y<=b;

WHEN "01" => x<=b; y<=c;

WHEN OTHERS => x<="0000"; y<="ZZZZ";

END CASE;

```

• Another important keyword is NULL: used when no action is to take place;

```

CASE identifier IS

WHEN value => assignments;

WHEN value => assignments;

...

END CASE;

```

#### Example

```

CASE control IS

WHEN "00" => x<=a; y<=b;

WHEN "01" => x<=b; y<=c;

WHEN OTHERS => x<="0000"; y<="ZZZZ";

END CASE;</pre>

```

- Another important keyword is NULL: used when no action is to take place;

- CASE allows multiple assignments for each test condition, while WHEN allows only one.

#### Example

A 1-digit counter (from 0 to 9)

with a reset

#### Example

A 1-digit counter (from 0 to 9) with a reset

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY counter IS

PORT (clk, rst : IN STD_LOGIC;

digit : OUT INTEGER RANGE 0 TO 9);

END counter;

ARCHITECTURE counter OF counter IS

BEGIN

count: PROCESS(clk, rst)

VARIABLE temp : INTEGER RANGE 0 TO 10;

BEGIN

CASE rst TS

WHEN '1' => temp :=0:

WHEN '0' =>

IF (clk'EVENT AND clk='1') THEN

temp := temp + 1;

IF (temp=10) THEN temp := 0;

END IF:

END IF:

WHEN OTHERS => NULL:

digit <= temp;</pre>

END PROCESS count;

END counter;

```

### WAIT statement

It is a sequential statement to elapse time.

It appears in three forms:

WAIT UNTIL signal\_condition;

WAIT ON signal1 [, signal2, ... ];

WAIT FOR time;

### WAIT statement

It is a sequential statement to elapse time.

It appears in three forms:

WAIT UNTIL signal\_condition;

WAIT ON signal1 [, signal2, ... ];

WAIT FOR time;

#### Example

```

PROCESS -- no sensitivity list

BEGIN

WAIT UNTIL (clk'EVENT AND clk='1');

IF (rst='1') THEN

x <= "000000000";

ELSIF (clk'EVENT AND clk='1') THEN

x <= a;

END IF;

END PROCESS;

```

```

PROCESS -- no sensitivity list

BEGIN

WAIT ON clk, rst;

IF (rst='1') THEN

output <= "00000000";

ELSIF (clk'EVENT AND clk='1') THEN

output <= input;

END IF;

END PROCESS;

```

For simulation only:

WAIT FOR 5NS;

# LOOP statement

It is the *loop* sequential statement.

It appears in two forms:

```

[label:] FOR identifier IN range LOOP

(sequential statements)

END LOOP [label];

```

[label:] WHILE condition LOOP

(sequential statements)

END LOOP [label];

## LOOP statement

It is the loop sequential statement.

It appears in two forms:

```

[label:] FOR identifier IN range LOOP

(sequential statements)

END LOOP [label];

```

```

[label:] WHILE condition LOOP

(sequential statements)

END LOOP [label];

```

## Example

FOR/LOOP

```

FOR i IN 0 TO 5 LOOP

x(i) <= enable AND w(i+2);

y(0, i) <= w(i);

END LOOP;</pre>

```

## WHILE/LOOP

```

WHILE (i < 10) LOOP

WAIT UNTIL clk'EVENT AND clk='1';

i:=i+1;

(other statements)

END LOOP;

```

## LOOP statement

It is the loop sequential statement.

It appears in two forms:

```

[label:] FOR identifier IN range LOOP

(sequential statements)

END LOOP [label];

```

```

[label:] WHILE condition LOOP

(sequential statements)

END LOOP [label];

```

## Example

FOR/LOOP

```

FOR i IN 0 TO 5 LOOP

x(i) <= enable AND w(i+2);

y(0, i) <= w(i);

END LOOP;</pre>

```

## WHILE/LOOP

```

WHILE (i < 10) LOOP

WAIT UNTIL clk'EVENT AND clk='1';

i:=i+1;

(other statements)

END LOOP;

```

• Limits of the range of FOR/LOOP must be static;

## LOOP statement

It is the loop sequential statement.

It appears in two forms:

```

[label:] FOR identifier IN range LOOP

(sequential statements)

END LOOP [label];

```

```

[label:] WHILE condition LOOP

(sequential statements)

END LOOP [label];

```

#### Example

## FOR/LOOP

```

FOR i IN 0 TO 5 LOOP

x(i) <= enable AND w(i+2);

y(0, i) <= w(i);

END LOOP;</pre>

```

## WHILE/LOOP

```

WHILE (i < 10) LOOP

WAIT UNTIL clk'EVENT AND clk='1';

i:=i+1;

(other statements)

END LOOP;</pre>

```

- Limits of the range of FOR/LOOP must be static;

- There exists a statement to exit the loop (EXIT), and a statement to skip loop steps (NEXT).

# VHDL

Composition

# Composition

Idea Compose basic "brick" of code in order to build bigger system.

#### Idea

Compose basic "brick" of code in order to build bigger system.

## Benefits

- Reusability of code;

- More understandable code;

- Modularity;

#### Idea

Compose basic "brick" of code in order to build bigger system.

## Benefits

- Reusability of code;

- More understandable code;

- Modularity;

## How to do it in VHDL

- COMPONENT;

- FUNCTION;

- PROCEDURE.

## Definition

**COMPONENT** = conventional code (**LIBRARY** declarations + **ENTITY** + **ARCHITECTURE**).

Declare a **COMPONENT** make it usable within another circuit, thus allowing the construction of *hierarchical* designs.

### Definition

**COMPONENT** = conventional code (**LIBRARY** declarations + **ENTITY** + **ARCHITECTURE**).

Declare a **COMPONENT** make it usable within another circuit, thus allowing the construction of *hierarchical* designs.

## Declaration

```

COMPONENT component_name IS

PORT (

port_name : signal_mode signal_type;

port_name : signal_mode signal_type;

...);

END COMPONENT;

```

#### Definition

**COMPONENT** = conventional code (**LIBRARY** declarations + **ENTITY** + **ARCHITECTURE**).

Declare a **COMPONENT** make it usable within another circuit, thus allowing the construction of *hierarchical* designs.

#### Declaration

```

COMPONENT component_name IS

PORT (

port_name : signal_mode signal_type;

port_name : signal_mode signal_type;

...);

END COMPONENT;

```

#### Instantiation

label: component\_name PORT MAP (port\_list);

## Example

## Example

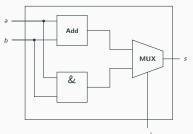

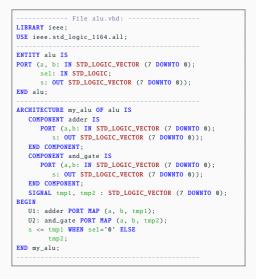

#### Example

```

File and_gate.vhd:

LIRRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY and_gate IS

PORT (a, b: IN STD_LOGIC_VECTOR (7 DOWNTO 0));

s: OUT STD_LOGIC_VECTOR (7 DOWNTO 0));

END and_gate

ARCHITECTURE my_and_gate OF and_gate IS

BEGIN

...

END my_and_gate

```

Example

sel

## Definition

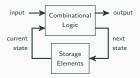

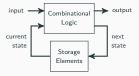

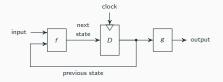

A state machine is a mathematical model used for designing sequential logic circuits.

#### Definition

A state machine is a mathematical model used for designing sequential logic circuits.

# $rac{c}{s_1}$

#### Implementation

- combinational:

- *next state* = f(input, previous state)

- *output* = g(input, previous state)

- a *sequential* part to synchronize the *state* changing.

## Moore Machine

- combinational:

- *next state* = f(input, previous state)

- *output* = g(previous state)

- sequential: D flip-flop.

## Moore Machine

- combinational:

- *next state* = f(input, previous state)

- *output* = g(previous state)

- sequential: D flip-flop.

## Mealy Machine

- combinational:

- *next state* = f(input, previous state)

- *output* = g(input, previous state)

- sequential: D flip-flop.

## Moore Machine

```

ENTITY moore machine IS

PORT (input: IN <data_type_in>;

clk: IN STD LOGIC:

output: OUT <data type out>):

END moore machine:

ARCHITECTURE my_moore OF moore_machine IS

COMPONENT f IS

PORT (input: IN <data type in>:

previous state: IN <data type state>:

next_state: OUT <data_type_state>);

END COMPONENT;

COMPONENT g IS

PORT (current state: IN <data type state>:

output: OUT <data type out>):

END COMPONENT:

SIGNAL p_state, n_state: <data_type_state>;

BEGIN

PROCESS (clk)

REGIN

IF (clk'EVENT AND clk='1')

p_state <= n_state;</pre>

END IF:

END PROCESS:

U1: f PORT MAP (input, p_state, n_state);

U2: g PORT MAP (n state, output);

END my moore:

```

## Moore Machine

```

ENTITY moore machine IS

PORT (input: IN <data_type_in>;

clk: IN STD LOGIC:

output: OUT <data type out>):

END moore machine:

ARCHITECTURE my_moore OF moore_machine IS

COMPONENT f IS

PORT (input: IN <data type in>:

previous state: IN <data type state>:

next state: OUT <data type state>):

END COMPONENT:

COMPONENT q IS

PORT (current state: IN <data type state>:

output: OUT <data type out>):

END COMPONENT:

SIGNAL p_state, n_state: <data_type_state>;

BEGIN

PROCESS (clk)

REGIN

IF (clk'EVENT AND clk='1')

p state <= n state:</pre>

END IF:

END PROCESS:

U1: f PORT MAP (input, p_state, n_state);

U2: g PORT MAP (n state, output);

END my moore:

```

#### Mealy Machine

```

ENTITY mealy machine IS

PORT (input: IN <data type in>:

clk: IN STD LOGIC:

output: OUT <data_type_out>);

END mealy_machine;

ARCHITECTURE my mealy OF mealy machine IS

COMPONENT F IS

PORT (input: IN <data_type_in>;

previous_state: IN <data_type_state>;

next_state: OUT <data_type_state>);

END COMPONENT.

COMPONENT a IS

PORT (input: IN <data type in>:

current_state: IN <data_type_state>;

output: OUT <data_type_out>);

END COMPONENT:

SIGNAL p state. n state: <data type state>:

REGIN

PROCESS (clk)

BEGIN

IF (clk'EVENT AND clk='1')

p_state <= n_state;</pre>

END IF:

END PROCESS:

U1: f PORT MAP (input, p state, n state):

U2: g PORT MAP (input, n_state, output);

END my_mealy;

```

# Conclusion

• Classical logic gates, and their truth tables;

- Classical logic gates, and their truth tables;

- Simplify boolean expression using properties of the algebra, and Morgan's Laws;

- Classical logic gates, and their truth tables;

- Simplify boolean expression using properties of the algebra, and Morgan's Laws;

- Design simple logical circuit given a specification.

- Classical logic gates, and their truth tables;

- Simplify boolean expression using properties of the algebra, and Morgan's Laws;

- Design simple logical circuit given a specification.

- Classical logic gates, and their truth tables;

- Simplify boolean expression using properties of the algebra, and Morgan's Laws;

- Design simple logical circuit given a specification.

## VHDL

• Structure of a VHDL file;

- Classical logic gates, and their truth tables;

- Simplify boolean expression using properties of the algebra, and Morgan's Laws;

- Design simple logical circuit given a specification.

- Structure of a VHDL file;

- Representation of data, and Data Types in VHDL;

- Classical logic gates, and their truth tables;

- Simplify boolean expression using properties of the algebra, and Morgan's Laws;

- Design simple logical circuit given a specification.

- Structure of a VHDL file;

- Representation of data, and Data Types in VHDL;

- Basic operators;

- Classical logic gates, and their truth tables;

- Simplify boolean expression using properties of the algebra, and Morgan's Laws;

- Design simple logical circuit given a specification.

- Structure of a VHDL file;

- Representation of data, and Data Types in VHDL;

- Basic operators;

- Concurrent code: the WHEN and GENERATE statements;

#### **Boolean Algebra**

- Classical logic gates, and their truth tables;

- Simplify boolean expression using properties of the algebra, and Morgan's Laws;

- Design simple logical circuit given a specification.

### VHDL

- Structure of a VHDL file;

- Representation of data, and Data Types in VHDL;

- Basic operators;

- Concurrent code: the WHEN and GENERATE statements;

- Sequential code: write a PROCESS using VARIABLE and the IF, WAIT, CASE and LOOP statements;

#### **Boolean Algebra**

- Classical logic gates, and their truth tables;

- Simplify boolean expression using properties of the algebra, and Morgan's Laws;

- Design simple logical circuit given a specification.

### VHDL

- Structure of a VHDL file;

- Representation of data, and Data Types in VHDL;

- Basic operators;

- Concurrent code: the WHEN and GENERATE statements;

- Sequential code: write a PROCESS using VARIABLE and the IF, WAIT, CASE and LOOP statements;

- Composition: use **COMPONENT**;

#### **Boolean Algebra**

- Classical logic gates, and their truth tables;

- Simplify boolean expression using properties of the algebra, and Morgan's Laws;

- Design simple logical circuit given a specification.

### VHDL

- Structure of a VHDL file;

- Representation of data, and Data Types in VHDL;

- Basic operators;

- Concurrent code: the WHEN and GENERATE statements;

- Sequential code: write a PROCESS using VARIABLE and the IF, WAIT, CASE and LOOP statements;

- Composition: use COMPONENT;

- Simulation: write a Simulation File in VHDL.

### State machine

### State machine

• Definition of State machine;

### State machine

- Definition of State machine;

- Mealy and Moore machine;

### State machine

- Definition of State machine;

- Mealy and Moore machine;

- Implementation of Mealy and Moore machine in VHDL;

### State machine

- Definition of State machine;

- Mealy and Moore machine;

- Implementation of Mealy and Moore machine in VHDL;

### Examples

• Half Adder and Full Adder;

### State machine

- Definition of State machine;

- Mealy and Moore machine;

- Implementation of Mealy and Moore machine in VHDL;

- Half Adder and Full Adder;

- *n* bits Adder;

### State machine

- Definition of State machine;

- Mealy and Moore machine;

- Implementation of Mealy and Moore machine in VHDL;

- Half Adder and Full Adder;

- *n* bits Adder;

- SR flip-flop;

### State machine

- Definition of State machine;

- Mealy and Moore machine;

- Implementation of Mealy and Moore machine in VHDL;

- Half Adder and Full Adder;

- *n* bits Adder;

- SR flip-flop;

- D flip-flop;

### State machine

- Definition of State machine;

- Mealy and Moore machine;

- Implementation of Mealy and Moore machine in VHDL;

- Half Adder and Full Adder;

- *n* bits Adder;

- SR flip-flop;

- D flip-flop;

- Multiplexer;

### State machine

- Definition of State machine;

- Mealy and Moore machine;

- Implementation of Mealy and Moore machine in VHDL;

- Half Adder and Full Adder;

- *n* bits Adder;

- SR flip-flop;

- D flip-flop;

- Multiplexer;

- Barrel shifter;

### State machine

- Definition of State machine;

- Mealy and Moore machine;

- Implementation of Mealy and Moore machine in VHDL;

- Half Adder and Full Adder;

- *n* bits Adder;

- SR flip-flop;

- D flip-flop;

- Multiplexer;

- Barrel shifter;

- Counter;

### State machine